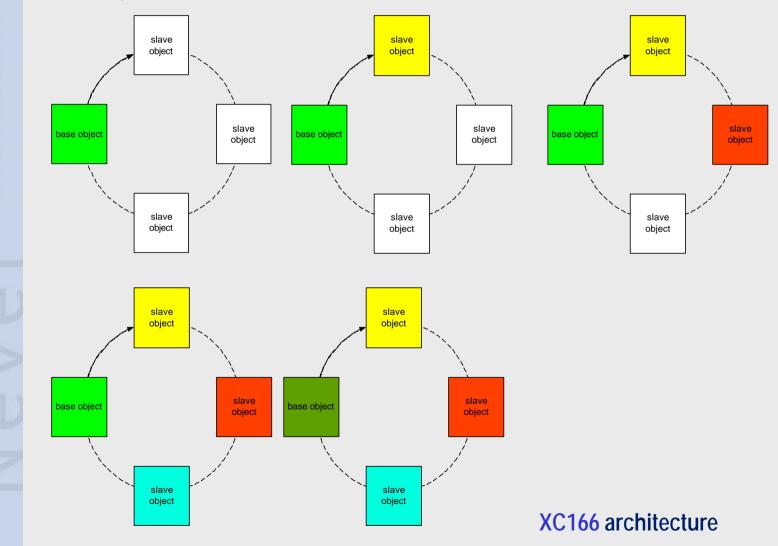

## XC166 architecture

## **TwinCAN**

#### TwinCAN: basics

- Enabled after startup

- Assignable to port 4, (7) or 9.

- Compatible to 32bit module

- Difference to old 16bit CAN:

- Additional node

- More message objects

- Mask on each message object

- All message objects are receive/transmit configurable

- FIFO/Gateway functionality

#### Short: More features.

AI MC MA TM

Juli, 02 Page 3

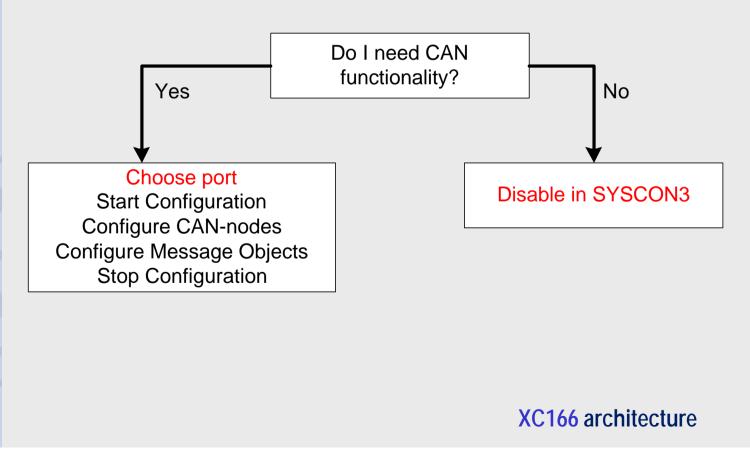

#### TwinCAN: getting started

#### Configurationflow

## TwinCAN: configuration in short

- Choose port: Set CAN\_PISEL, the corresponding ALTSEL register(s) and DPx.

- Start configuration: xCR := 0x41

- Configure the CAN nodes, like you need them

- Configure the message objects

- Stop configuration: CAN node not needed xCR:=1 CAN node needed: xCR := (0x00xxx00)<sub>b</sub>

- CAN action is able to start.

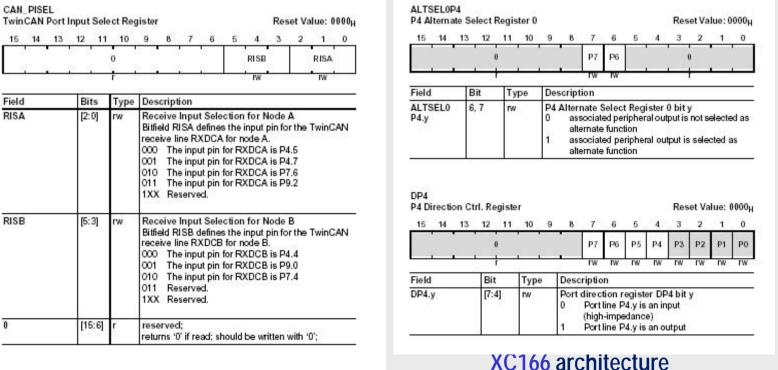

# CAN\_PISEL TwinCAN PA

## TwinCAN configuration of ports

- Choose port: Set CAN\_PISEL, the corresponding ALTSEL register(s) and DPx.

- CAN\_PISEL configure the receive pins for the CAN.

- ALTSELPx configure the port pin to be a special function pin.

#### - DPx configure the direction of the port pin.

AI MC MA TM Juli, 02 Page 6

## TwinCAN configure the nodes

Start configuration: xCR := 0x41

#### Configure the CAN nodes, like you need them

| BCR | M 0 | ontro | /1 15.6 | s Airo | s r ceit |    |    |   |   |     |     |   |     | 1,00.0 | et Va | ue.              | 0001              |

|-----|-----|-------|---------|--------|----------|----|----|---|---|-----|-----|---|-----|--------|-------|------------------|-------------------|

|     | ВС  | ontro | el Re   | egis   | ter      |    |    |   |   |     |     |   |     | Res    | et Va | ue:              | 0001 <sub>1</sub> |

| 15  | 14  | 13    | 12      | 2      | 11       | 10 |    | 9 | 8 | 7   | 6   | Б | 4   | 3      | 2     | $\mathbb{R}^{2}$ | 0                 |

| 18  |     |       | 25      |        | 1        |    | 85 |   |   | CAL | CCE | 0 | LEC | EIE    | SIE   | 0                | INIT              |

- CALM: Analyzer Mode, listening to the bus, receiving messages, but never answering

- LECIE, EIE, SIE: status and error interrupts enable

- CCE: Enable access to bittiming registers, disable modification of error counters.

- INIT: Stops all CAN traffic, access to configuration registers is enabled, reset starts bus synchronization procedure.

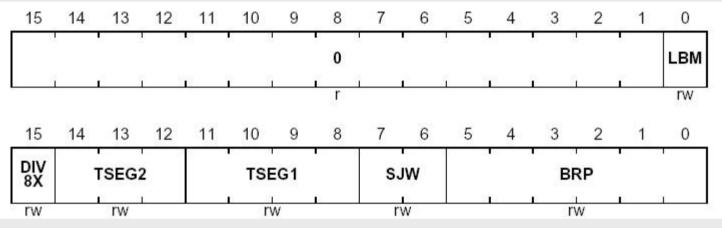

## TwinCAN, configure the nodes

#### Bittiming register xBTRH/L

- LBM: Loop Back Mode (Internal connection, no outside signal)

- DIV8x: Additional Divider of 8 for fCAN

- TSEG2, TSEG1, SJW: Define Sampling Point

- BRP: Baudrate Prescaler

## TwinCAN, configure the nodes

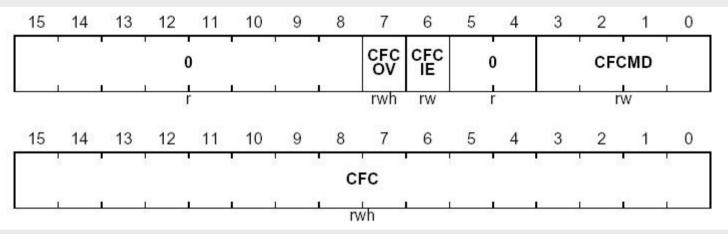

#### Configure the Frame Counter xFCRH/L

- Interesting for analyzing purposes or time stamp systems

- CFCMD: Frame Counter Mode

- CFCOV/CFCIE: In case of overflow, define action

## TwinCAN, configure the nodes

- Interrupt characteristics and reaction

- xGINP: Which interrupt is related for which node

- Define Interrupt Characteristics concerning node interrupt source numbers

- xIMRH/L0/4: Interrupt Mask Register for message objects

- Define the message objects, where an interrupt shell get through or not

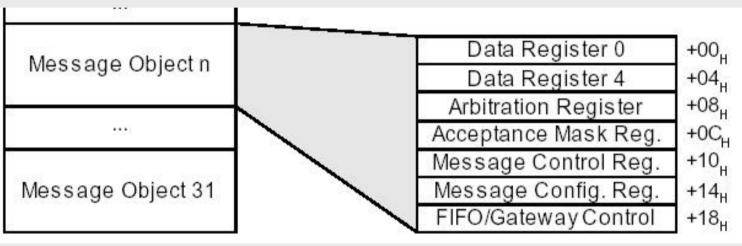

#### Message Object Overview

- MSGDRH/Lx0/4: Data Registers

- MSGARH/Lx: Arbitration Register containing the message identifier

- MSGAMRH/Lx: Arbitration Mask, 1 means, that the bit in the ID is taken into account for acceptance, 0 otherwise.

AI MC MA TM Juli, 02 Page 10

ALMC MA TM Juli. 02 Page 11

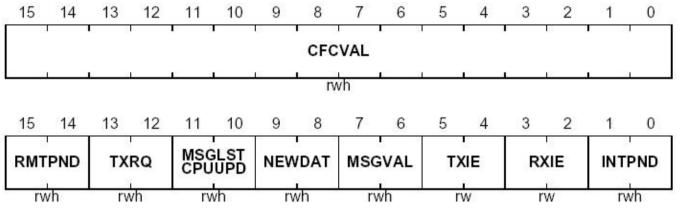

#### MSGCTRH/Ln: Message Control Register

| 15     | 14 | 13      | 12 | 11         | 10               | 9  | 8      | 7   | 6   | 5    | 4   | 3    | 2  | 1      | 0  |

|--------|----|---------|----|------------|------------------|----|--------|-----|-----|------|-----|------|----|--------|----|

|        |    |         |    |            |                  |    | CFC    | VAL |     |      |     |      |    |        |    |

| 2      |    |         |    |            |                  |    | rv     | /h  |     |      | C 3 |      | 65 |        | I  |

| 15     | 14 | 13      | 12 | 11         | 10               | 9  | 8      | 7   | 6   | 5    | 4   | 3    | 2  | 1      | 0  |

| RMTPND |    | ND TXRQ |    | MSG<br>CPU | MSGLST<br>CPUUPD |    | NEWDAT |     | VAL | TXIE |     | RXIE |    | INTPND |    |

| rw     | /h | rw      | /h | rv         | vh               | rv | /h     | rv  | /h  | r    | N   | r    | w  | rv     | vh |

- INTPND: Interrupt Pending, shows if an interrupt is pending for this message object (reset by software!). Slow update!

- RXIE/TXIE: Define interrupt enable

- Tag message object to be valid or unvalid for changes. Set in order to take into account an update of bits XTD, DIR, NODE and CANPTR.

#### MSGCTRH/Ln: Message Control Register

| 15  | 14  | 13 | 12 | 11         | 10         | 9    | 8   | 7   | 6   | 5  | 4   | 3  | 2   | 1   | 0   |

|-----|-----|----|----|------------|------------|------|-----|-----|-----|----|-----|----|-----|-----|-----|

|     |     |    |    |            |            |      | CFC | VAL |     |    |     |    |     |     |     |

|     |     |    |    | L - 1      |            | 15 5 | rw  | /h  |     |    |     |    | 15  |     | L   |

| 15  | 14  | 13 | 12 | 11         | 10         | 9    | 8   | 7   | 6   | 5  | 4   | 3  | 2   | 1   | 0   |

| RMT | PND | тх | RQ | MSG<br>CPU | LST<br>UPD | NEW  | DAT | MSG | VAL | тх | (IE | R) | (IE | INT | PND |

| rw  | rwh |    | vh | rw         | /h         | rv   | vh  | rv  | /h  | r  | N   | r  | w   | rv  | vh  |

#### • NEWDAT:

For Tx-Objects, this bitfield is supposed to be set by software. It indicates, that the contents is ready for sending and needs to be set to allow the message, to be copied into the bitstream.

For Rx-Objects, this bitfield is set by hardware, to indicate, that a message has been received. This bit has to be reset by software. In case this bitfield is still set on NEWDAT and an additional message comes in for this object, a message loss will be indicated.

#### MSGCTRH/Ln: Message Control Register

| 15  | 14  | 13 | 12 | 11         | 10         | 9    | 8   | 7   | 6   | 5  | 4   | 3  | 2  | 1   | 0   |

|-----|-----|----|----|------------|------------|------|-----|-----|-----|----|-----|----|----|-----|-----|

|     |     |    |    |            |            |      | CFC | VAL |     |    |     |    |    |     |     |

| 2   |     |    | I  | L          |            | 15 5 | rv  | vh  |     |    |     |    |    |     | I   |

| 15  | 14  | 13 | 12 | 11         | 10         | 9    | 8   | 7   | 6   | 5  | 4   | 3  | 2  | 1   | 0   |

| RMT | PND | тх | RQ | MSG<br>CPU | LST<br>UPD | NEW  | DAT | MSG | VAL | тх | (IE | R) | ίE | INT | PND |

| rw  | /h  | rv | vh | rv         | /h         | rv   | vh  | rv  | /h  | r  | N   | r  | w  | rv  | vh  |

MSGLST/CPUUPD:

MSGLST: Indicates, that a new message has been received during NEWDAT is still set for this message object. This bit has to be reset by software.

CPUUPD: This bit shall be set by software, to indicate, that transmission is forbidden, due to current changes on the message object.

#### MSGCTRH/Ln: Message Control Register

- TxRQ: Message is ready for transmission.

- RMTPND: Set for transmission objects, in case a remote request is still pending. TxRQ will be set as well.

- **General remark:** On this message object no direct move takes place. All bits will be changed by a logical bitwise AND.

MSGCFGH/Lx: Message Configuration Register

AI MC MA TM Juli, 02 Page 15

#### 15 13 12 11 10 5 2 14 9 8 6 4 3 1 0 TXINP RXINP 0 0 rw rw 15 3 2 14 13 12 11 10 9 8 6 5 4 1 0 DLC DIR XTD 0 rwh rwh rw rwh rw

- RMM: Remote Monitoring Enable, in case the the identifier and the number of data bytes are copied into the remote frame. Only valid for transmit objects.

- NODE: Message object belongs to node A or B.

- XTD and DLC: Characteristics of message

- DIR: Receive or Transmit Object.

- RXINP, TXINP: Interrupt Source linked to this message object.

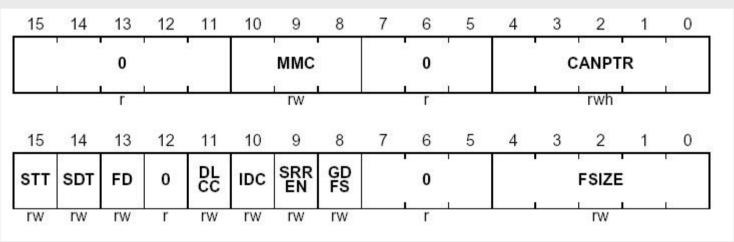

MSGFGCRH/Lx: FIFO/Gateway Control Register

MMC: Message Object Mode Control Bitfield MMC controls the functionality of message object x. The user can choose between standard message object, FIFO (depending on the function and the position base or slave), normal gateway or shared gateway (receive side - depending on the position).

MSGFGCRH/Lx: FIFO/Gateway Control Register

| 15  | 14    | 13 | 12 | 11       | 10  | 9         | 8        | 7  | 6 | 5 | 4      | 3 | 2     | 1 | 0 |  |  |

|-----|-------|----|----|----------|-----|-----------|----------|----|---|---|--------|---|-------|---|---|--|--|

|     | 0 MMC |    |    |          |     |           |          |    | 0 |   | CANPTR |   |       |   |   |  |  |

|     | []    | r  | I  | 1        |     | rw        | Ĺ        |    | r | 1 |        |   | rwh   | í |   |  |  |

| 15  | 14    | 13 | 12 | 11       | 10  | 9         | 8        | 7  | 6 | 5 | 4      | 3 | 2     | 1 | 0 |  |  |

| STT | SDT   | FD | 0  | DL<br>CC | IDC | SRR<br>EN | GD<br>FS |    | 0 | I | 2      |   | FSIZE |   |   |  |  |

| rw  | rw    | rw | r  | rw       | rw  | rw        | rw       | 32 | r |   |        |   | rw    |   |   |  |  |

- CANPTR: CAN Pointer for FIFO/Gateway Functions depending on the value in MMC. In case an invalid or a wrong value is set in this register, no FIFO or normal gateway will work!

- SDT/STT: One shot modes. SDT, MSGVAL will be reset in case of bit set. STT, no automatic retransmission will take place.

#### MSGFGCRH/Lx: FIFO/Gateway Control Register

| 15  | 14  | 13 | 12 | 11       | 10       | 9         | 8        | 7 | 6 | 5 | 4 | 3      | 2     | 1 | 0         |  |  |  |

|-----|-----|----|----|----------|----------|-----------|----------|---|---|---|---|--------|-------|---|-----------|--|--|--|

|     | 0   |    |    |          |          | ммс       |          |   | 0 |   |   | CANPTR |       |   |           |  |  |  |

|     | Ê   | r  |    | 1        | <u> </u> | rw        | Ĺ        |   | r |   |   | i      | rwh   | ĩ | <u>[]</u> |  |  |  |

| 15  | 14  | 13 | 12 | 11       | 10       | 9         | 8        | 7 | 6 | 5 | 4 | 3      | 2     | 1 | 0         |  |  |  |

| STT | SDT | FD | 0  | DL<br>CC | IDC      | SRR<br>EN | GD<br>FS |   | 0 |   |   |        | FSIZE |   |           |  |  |  |

| rw  | rw  | rw | r  | rw       | rw       | rw        | rw       |   | r |   |   |        | rw    | I |           |  |  |  |

- FD: FIFO direction, defines update event of FIFO.

- IDC: Copy identifier in case of gateway function to the destination bus.

- SRREN: Remote requests pass the gateway.

- GDFS: Gateway function is complete done by hardware.

- FSIZE: length of FIFO.

XC166 architecture

AI MC MA TM

Juli, 02 Page 19

## TwinCAN, configure the message objects.

- Filling the FIFO buffer

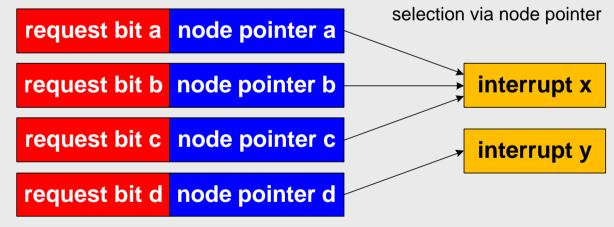

## TwinCAN, Interrupts

- Up to eight individually programmable interrupt nodes can be used.

- 32 interrupts assignable to message objects of node A as well as to B plus four interrupt sources for each node.

#### Concept:

Do not use INTPND, use TXPND and RXPND!

AI MC MA TM Juli, 02 Page 20