Mikroelektronik

Herstellung integrierter Schaltkreise

Karl-Wilhelm Baier

Literatur

Bezugsquellen

Nützliche Links

Die Entwicklung der Mikroelektronik demonstriert die Leistungsfähigkeit

der Halbleiterelektronik in eindrucksvoller Weise. Strukturgrößen von 350

Nanometern galten vor einigen Jahren noch als unerreichbar.

In der ersten Generation elektronischer Bauteile, die bis in die sechziger

Jahre reichte, standen Bauelemente zur Verfügung, die jeweils nur eine

einzige definierte Eigenschaft hatten: Spulen als Induktivitäten, Kondensatoren

als Kapazitäten, Dioden als Gleichrichter, Widerstände, Transistoren als

Verstärker.

In der ersten Generation elektronischer Bauteile, die bis in die sechziger

Jahre reichte, standen Bauelemente zur Verfügung, die jeweils nur eine

einzige definierte Eigenschaft hatten: Spulen als Induktivitäten, Kondensatoren

als Kapazitäten, Dioden als Gleichrichter, Widerstände, Transistoren als

Verstärker.

Bei der Entwicklung einer Schaltung mußten die zur Verfügung stehenden

Bauteile zu einem funktionsfähigen Gebilde entsprechend den einzelnen Kenndaten

zusammengebaut werden. Da Transistoren und Dioden aus dem gleichen Werkstoff,

Silizium oder Germanium, bestehen, begann man allmählich, viele gleichartige

Bauelemente gemeinsam auf einer Scheibe herzustellen. Durch Auseinanderbrechen

der Scheibe erhielt man dann wieder einzelne Bauelemente. Schließlich erkannte

man die Möglichkeit, auch Widerstände und Kondensatoren auf Siliziumbasis

herzustellen. Der Schritt, bereits eine komplette Schaltung auf einer Siliziumscheibe

zu konzipieren, und diese Scheibe dann nicht mehr in einzelne Bauelemente

zu zerbrechen, war dann nicht mehr weit.

Die auf diese Weise entstandenen integrierten Schaltkreise (IC von Integrated

Circuit) hatten mehrere Vorteile:

wesentlich geringerer Raumbedarf,

geringeres Gewicht,

geringerer Herstellungsaufwand,

erhöhte Zuverlässigkeit, da weniger Lötstellen, und

deutlich geringere Herstellungskosten.

Erste, in Serie hergestellte IC hatten fünf bis sechs Transistorfunktionen.

Insbesondere die drastisch sinkenden Herstellungskosten bewirken die Erschließung

immer neuer Anwendungsgebiete für hochintegrierte Schaltungen. Dabei wird

jedoch mit zunehmender Komplexität einer integrierten Schaltung ihre Funktion

und damit zumeist auch ihr Anwendungsbereich immer spezieller. Infolgedessen

bleiben die Stückzahlen dieser IC niedrig, die Kosten steigen damit aber

wieder an. Ein IC, der dieses Problem umgeht, also ein besonders großes

Anwendungsgebiet hat, ist der Mikroprozessor.

In den folgenden Abschnitten werden einige grundlegende Schritte, die zur

Herstellung von integrierten Schaltkreisen nötig sind, beschrieben.

Es gibt zwei verschiedene Systeme:

bipolare Schaltungen und

MOS-Schaltungen.

Beide Schaltungen sind sog. „monolithische“ integrierte Schaltungen, d.

h. alle Schaltungselemente und ihre Verbindungen werden in einem gemeinsamen

Fertigungsprozeß (Planartechnik) auf einem einkristallinen Siliziumplättchen

(Chip) hergestellt.

Bipolare Schaltungen arbeiten mit stromgesteuerten Transistoren, MOS-Schaltungen

dagegen mit spannungsgesteuerten Transistoren. Da den MOS-Schaltungen der

etwas einfachere Herstellungsprozeß zugrunde liegt, sollen nur diese beschrieben

werden.

Benötigt man in einer Schaltung keine Induktivitäten, so kommt man mit

einem einzigen Bauteil aus, dem MOS-Transistor (Metal-Oxide-Semiconductor).

Je nach Verschaltung erhält man mit ihm eine Kapazität oder einen nichtlinearen

Widerstand.

Zum besseren Verständnis des Herstellungsprozesses von MOS-Schaltungen

sollen zunächst einige Grundlagen zur Transistorfunktion aufgezeigt werden.

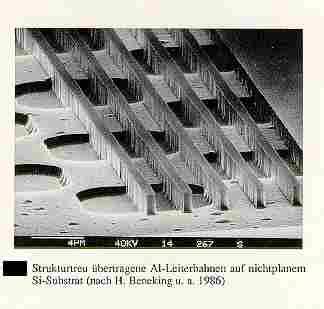

Der n-Kanal-MOS-Feldeffekttransistor

In ein p-leitendes Gebiet werden zwei n-leitende Gebiete eingelassen. Man

bezeichnet die beiden n-Gebiete mit Source (Quelle) und Drain (Senke).

Auf diese Weise erhält man von links einen n-p-Übergang, von rechts ebenso,

Abbildung 1. Wird nun an Source und Drain eine Spannung angelegt, so sperrt

immer ein n-p-Übergang, unabhängig von der Polung der Spannung, d. h. bei

Pluspol an Source sperrt der rechte n-p-Übergang, bei Minuspol an Source

sperrt der linke n-p-Übergang.

Über einen dritten Anschluß, das Gate (Tor), läßt sich diese Sperrwirkung

aufheben.

Ist das Gate gegenüber den dotierten Gebieten isoliert, so bewirkt eine

dort angelegte positive Spannung ein Wegrücken der Löcher im p-Gebiet.

Gleichzeitig werden Elektronen an die Isolierschicht des Gate gezogen.

Es entsteht also unterhalb der Isolierschicht ein schmaler Kanal, der an

positiven Ladungsträgern verarmt, mit negativen Ladungsträgern aber angereichert

ist: Es bildet sich ein negativ leitendes Gebiet (n-Kanal).

Somit werden aus den n-p-n-Übergängen n-n-n-Übergänge. Es existiert keine

Sperrschicht mehr; zwischen Source und Drain kann Strom fließen. Die Breite

des n-Kanals, und damit die Größe des Stroms zwischen Source und Drain

ist abhängig von der Größe der Gatespannung.

Auf diese Weise erhält man ein Bauelement, bei dem ein Stromfluß über eine

angelegte Spannung gesteuert werden kann, den MOS-Transistor.

Herstellungstechniken

Es gibt verschiedene Methoden zur Herstellung von MOS-Transistoren. Als

Beispiel sei die Aluminium-Gate-Technik mit n-Kanal beschrieben, zumal

sich andere Techniken in ihren prinzipiellen Abläufen davon nicht unterscheiden.

Ein CMOS - Prozeß kann auf dieser Basis leicht, durch Erweiterung der Prozeßschritte,

erklärt werden.

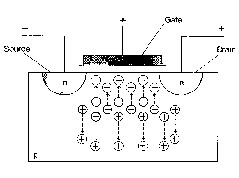

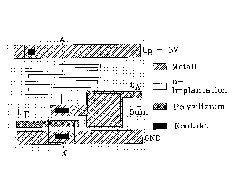

Der MOS-Prozeß ist ein Planarprozeß, d. h. es werden alle Fertigungsschritte

von der Oberfläche her durchgeführt. Zur Erläuterung der einzelnen Arbeitsabläufe

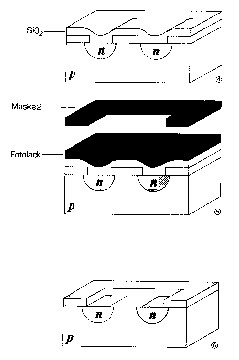

dient Abbildung 2. Ausgangsmaterial für den MOS-Prozeß ist eine polierte

p-dotierte (Hochtemperaturdiffusion mit BBr3-Bor) Siliziumscheibe mit einem

Durchmesser von bis zu 200 mm und einer Dicke von 200-450 m (1µm =1/1000mm),

der sog. Wafer. Im ersten Schritt wird auf diese Scheibe eine 0,3 µm dicke

Siliziumdioxid-Schicht (Si02) aufgebracht. Dies geschieht in einem Oxidationsofen,

in dem die Scheibe bis zu zwei Stunden einer feuchten, auf etwa 1000°C

erhitzten Sauerstoff-Atmosphäre ausgesetzt wird. Als nächstes werden die

Diffusionsgebiete für Source und Drain vorbereitet. Dies geschieht durch

eine Maske 1, eine Photoplatte, die bis auf die Stellen, an denen sich

Source und Drain befinden sollen, geschwärzt ist. Die oxidierte Scheibe

wird mit einem Photolack versehen und durch die Maske 1 mit ultraviolettem

Licht belichtet Abbildung 2-1.

Beim nachfolgenden Entwickeln und Wässern wird der Photolack an den belichteten

Stellen abgelöst; an den unbelichteten Stellen bleibt er als Schutzschicht

auf dem Wafer. Die so behandelte Scheibe taucht man einige Minuten in ein

Flußsäurebad, in dem die nicht vom Photolack geschützte Siliziumdioxid-Schicht

weggeätzt wird (Abbildung 2-2). Nach diesen Vorbereitungen können Source-

und Drain-Gebiete hergestellt werden.

Zu diesem Zweck wird die Siliziumscheibe nach Entfernung des restlichen

Photolacks in einem Diffusionsofen bei über 1000°C einer phosphorhaltigen

Atmosphäre ausgesetzt (Diffusionsschritt). Während die Scheibe anschließend

wieder einer feuchten, reinen Sauerstoffatmosphäre ausgesetzt wird, kann

der Phosphor an den oxidfreien Stellen in das Silizium eindiffundieren

(Abbildung 2-3).

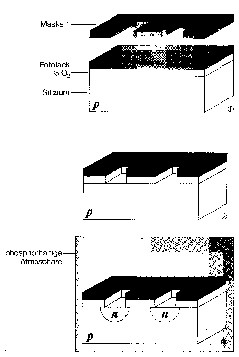

In der p-dotierten Siliziumscheibe liegen jetzt die n-dotierten Gebiete

für Source und Drain vor. Durch die feuchte Sauerstoffatmosphäre hat sich

aber auf der gesamten Oberfläche eine neue Oxidschicht gebildet - 0,8µm

(Abbildung 3-4).

Mit Hilfe einer Maske 2 wird das Oxid an den Stellen weggeätzt, an denen

sich später die dünne Oxidschicht zur Isolation des Gate sowie die Anschlüsse

für Source und Drain befinden sollen (Abbildung 3-5). Die Maske 2 muß in eine solche

Lage gebracht werden, daß keine Verschiebungen zu den bereits durch Maske 1

aufgebrachten Strukturen auf der Scheibe entstehen. Dazu sind besondere

Justiermarken auf dem Silizium und auf

den Masken vorgesehen. Bei diesen Justiervorgängen muß mit bestimmten Toleranzen

gerechnet und dies bereits beim Entwurf berücksichtigt werden. Man rechnet mit

Justiertoleranzen bei 1m,

welche infolge zu Überlappungskapazitäten führen. Unterhalb des

Gate dürfen keine nicht steuerbaren Bereiche entstehen.

Nach dem Beschichten mit Photolack, Entwickeln, Wegätzen der Oxidschicht

und Entfernen des Photolacks (Abbildung 3-6) werden die freigelegten Gebiete mit einer 0,12-0,04 m dicken Oxidschicht versehen. Diese Oxidschicht, die

ja das Aluminium des Gate vom p-dotierten Silizium isolieren soll, muß

sehr exakt hergestellt werden, da sie die Funktionsfähigkeit des Transistors

beeinflußt. Ein Wegätzen der vorher an dieser Stelle vorhandenen Oxidschicht

bis auf die gewünschte Stärke läßt sich kaum genau durchführen. Daher wird

die gesamte Oxidschicht entfernt und eine neue Schicht exakt bis zur gewünschten

Dicke aufgebaut.

Hinweis:

Durch die Oxidation verarmt der p-Bereich an Bor, sodaß eine Ionenimplantation

mit Bor durch das Oxid hindurch durchgeführt wird. Mittels dieses Schrittes

kann zudem die Schwellenspannung der Transistoren eingestellt werden.

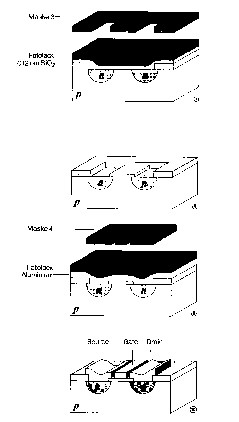

In einem weiteren photolithographischen Prozeß entfernt man das Oxid mit

Hilfe der Maske 3 (Abbildung 4-7) in

den Kontaktlöchern der n-Gebiete

(Abbildung

4-8). Anschließend wird die ganze

Scheibe mit einer etwa 1m dicken Aluminiumschicht

bedampft.

Abschließend wird photolithographisch mit Hilfe der Maske 4 (Abbildung

4-9) das Aluminium mit Phosphorsäure

an den Stellen weggeätzt, an denen es nicht benötigt wird. Man erhält dadurch

ein Aluminium-Muster auf dem Silizium, bestehend aus Verbindungsleitungen der

einzelnen MOS-Transistoren, den Kontaktierungen für Sources und Drains, den

Gates und den äußeren Anschlüssen (Abbildung 4-10).

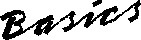

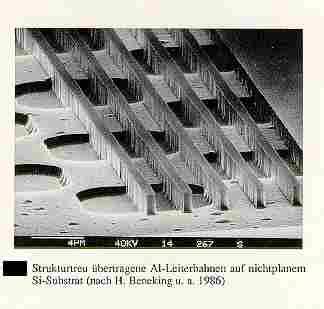

Der vorgestellte Prozeß geht davon aus, daß sich Verbindungsleitungen nicht

kreuzen. Ist dies nicht möglich, so bieten sich mehrere Verfahren an. z.B.:

Man bringt eine neue Oxidschicht auf und darauf erneut eine Aluminiumschicht.

Auf diese Weise läßt sich eine zweite Leitungsebene schaffen.

Unterwanderungen mittels dotierten Siliziumbahnen

Um den Wafer vor mechanischen Beschädigungen bei der weiteren Verarbeitung

zu schützen, wird eine letzte Oxidschicht aufgebracht und diese an den

Kontaktierungsflächen für die Anschlußdrähte wieder entfernt.

Nach diesem letzten chemotechnischen Vorgang wird die Scheibe in einen

Prüfautomaten gebracht. Dieser setzt Meßspitzen auf die Anschlußflächen

einer Schaltung und testet sie mit Hilfe eines Computerprogramms auf ihre

Funktionsfähigkeit. Stellt der Computer einen Funktionsausfall fest, erhält

die fehlerhafte Schaltung eine Farb-Markierung. Dabei kann sich herausstellen,

daß nur wenige Prozent der Schaltung den Funktionstest bestehen. Es ist

dann aber sehr schwierig festzustellen, wo die Ursache des Ausfalls zu

suchen ist. Daher spielen Kontrollen während des Herstellungsprozesses

eine große Rolle. So untersucht man Oxidschichten unter dem Mikroskop mit

Hilfe von Interferenzfarben. Man kann auf die Scheibe Teststrukturen bringen,

die während der Herstellung gemessen werden. Auch visuelle Inspektionen

werden an wichtigen Stellen der Fertigung durchgeführt.

Sind auf der Scheibe die funktionsfähigen Schaltungen markiert, so wird

diese mit einem Diamanten geritzt und durch anschließendes Brechen in die

einzelnen Schaltungen geteilt. Die funktionsfähigen Schaltungen werden

in ein Gehäuse geklebt. Schließlich verbindet man die Anschlußdrähte von

etwa 24 m Dicke durch Thermokompression mit dem Chip und verschließt das

Gehäuse. Weiters gibt es noch “Ultraschallbonden” und das “Thermosonic-Verfahren”

zur Einzeldraht-Kontaktierung und aber auch Komplettkontaktierungsverfahren.

Einige neuere Methoden und Größenordnungen:

Die Entwicklung von 256 Mbit/chip Speicherbausteinen demonstriert die Leistungsfähigkeit

der Halbleitertechnologie. Strukturgrößen von 0,35m Weite (z.B.: die Kanallänge

des FET), die noch vor wenigen Jahren bei Fotolithographieprozessen als

unerreichbar galten, werden zur Zeit in der Produktion eingesetzt.

Folgende Verfahren haben außerdem Wesentliches beigetragen:

LOCMOS-Technik (und auch SPOT-Technik oder SILO-Technik u.ä.)

“Lokale Oxidation von Silizium” - das Wegätzen der Oxidschicht an den unerwünschten

Stellen hat viele Nachteile und wird bei dieser Technik vermieden, was

eine höhere Integration erlaubt.

SOI-Techniken

“Silicon on Insulator” - Diese Techniken vermeiden eine Verschlechterung

der elektrischen Eigenschaften von MOS-Transistoren durch zunehmende Strukturfeinheit

und verringern die parasitären Kapazitäten.

Spacer-Technik

dient der Optimierung von Dotierungsbereichen.

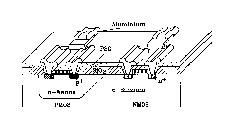

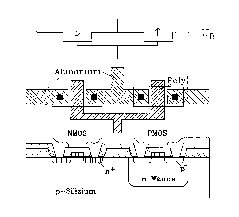

In Folge sehen Sie einen CMOS-Inverter hergestellt in der sogenannten “n-Wannen-Silizium-Gate

Technik”, welche zur Erklärung diesen Rahmen hier allerdings sprengen würde.

PSG - Phosphorsilikatglas

Dieses dient der Abflachung von Kanten.

Dotierungstechniken

Bei der Herstellung von ICs geht man von einer vordotierten Siliziumscheibe

aus. Diese Vordotierung ist möglich

beim Ziehen des Kristalls (Legierung) oder

durch Neutronenbestrahlung.

Beim erstgenannten Verfahren gibt man der erhitzten, zähflüssigen Siliziumschmelze

den Dotierstoff (z. B. Phosphor) zu. Beim Ziehen des Einkristalls bauen

sich die Dotieratome in das Kristallgitter des Siliziums ein. Man erhält

dadurch einen ca. 1,50 m langen, bis zu 10 cm dicken Siliziumstab, der

je nach Fremdatom p-dotiert oder n-dotiert ist. Durch scheibchenweises

Absägen erhält man die zur Herstellung von ICs benötigten Wafer.

Bei der Neutronenbestrahlung wandeln sich die Siliziumatome des Isotops

Si 30/14 durch Beschuß mit Neutronen in Phosphoratome um:

Si 30/14 + n — P 31/15 + e-.

Die damit erreichte Dotierung ist sehr gleichmäßig und läßt sich genau

steuern. Ein Nachteil ist die verhältnismäßig geringe Häufigkeit des Siliziumisotops.

Beim Herstellungsprozeß müssen genau umrissene Gebiete (Source und Drain)

dotiert werden; es wird also selektiv dotiert. Auch dafür gibt es verschiedene

Möglichkeiten:

Diffundieren,

Implantieren.

Die Dotierung durch Diffusion ist bereits vorher erläutert worden. Bei

der Ionenimplantation werden elektrisch geladene Teile (Ionen) eines gasförmigen

Dotierstoffs durch ein elektrisches Feld beschleunigt und in den Halbleiterkristall

hineingeschossen. Dieses Verfahren ermöglicht im Gegensatz zur Diffusion

eine besonders genaue Dosierung und Lokalisierung.

Herstellung der Masken

Sollen auf einem Siliziumplättchen von 5 mm x 5 mm Kantenlänge Hunderttausende

von Transistorfunktionen verwirklicht werden, so setzt dies entsprechend

feine Strukturen voraus. Hierdurch wird aber die Masken- und Phototechnik

zu einem Problem. Den Ausgangspunkt für die Maskenherstellung bildet immer

die Topographie einer Schaltung. Dies ist eine im Maßstab

100: 1 oder noch größer gezeichnete Vorlage der Schaltung. Diese Vorlage

steuert ein Lichtzeichengerät.

Bei der photographischen Maskentechnik steuert die Vorlage ein Zeichengerät,

das ein verkleinertes Abbild der Topographie auf einer Photoplatte wiedergibt.

Man nennt diese Photoplatte „Reticle“ (Abbildung 7).

Das Reticle hat bei einem Maßstab von 10:1 noch immer eine Kantenlänge

von 5 cm x 5 cm. In einer Wiederholkamera wird das Reticle noch einmal

zehnfach verkleinert auf eine Photoplatte gebracht, die die Abmessungen

des herzustellenden Wafers hat. Zusätzlich zur Verkleinerung lichtet die

Wiederholkamera aber Topographie neben Topographie auf der Photoplatte,

der sog. „Muttermaske“, ab. Auf dieser Muttermaske, von der Kopien als

Masken im Herstellungsprozeß verwendet werden, finden mehrere hundert ICs

Platz.

Mit Hilfe dieser Technik lassen sich nur Strukturen bei 1 µm herstellen.

Verwendet man dagegen Elektronenstrahlen, so lassen sich Strukturen herstellen,

die etwa um den Faktor 100 kleiner sind. Weiters gibt es noch die Röntgenstrahl-Lithographie,

andere befinden sich in Entwicklung.

Entwurfstechnik

Bevor eine integrierte Schaltung hergestellt werden kann, muß eine Vielzahl

von Schritten ablaufen, bei denen einige ohne Unterstützung durch Rechner

nicht mehr möglich sind. Dies gilt besonders für IC mit mehreren hunderttausend

Transistorfunktionen. Zu diesen rechnerunterstützten Schritten zählen besonders

die Entwicklung und Berechnung der Schaltung,

der geometrische Entwurf der Masken,

die Herstellung der Masken

Entwicklung und Berechnung der Schaltung

Anfangs ging man bei der Entwicklung von integrierten Schaltungen in althergebrachter

Art und Weise vor:

1. Die herzustellende Schaltung wurde in bereits bekannte Teilsysteme zerlegt,

die entsprechend verschaltet wurden.

2. Die Teilsysteme zerlegte man in Untersysteme, bis man auf der Ebene der

Einzelbauelemente angelangt war (Schaltplan).

3. Die Dimensionierung der einzelnen Bauelemente wurde auf Grund ihrer Funktionen

im Schaltplan berechnet.

4. Die gesamte Schaltung wurde mit Einzelbauelementen aufgebaut und auf

ihre gewünschte Funktion getestet.

Bei Schaltungen mit 1000, 10000 oder mehr Transistoren ist es nicht mehr

möglich, die Bauteiledimensionierung ohne Rechnerunterstützung durchzuführen.

Auch der Probeaufbau der gesamten Schaltung mit diskreten Bauelementen

würde wegen Geld- und Zeitmangels scheitern. Man ist daher dazu übergegangen,

die entwickelte Schaltung vom Rechner simulieren zu lassen.

Die Entwicklung von Programmen zur Simulation von integrierten Schaltungen,

die unter dem Begriff CAD zusammengefaßt sind, spielt daher eine große

Rolle. Aus der Reihe derartiger Programme sollen zwei näher erläutert werden.

A) Netzwerkanalyseprogramm

Unter Netzwerkanalyse versteht man die analoge Simulation elektrischer

Schaltungen; d. h. die einzelnen Bauelemente werden durch Modelle ersetzt.

Es lassen sich dabei physikalische Modelle, mathematische Modelle oder

Netzwerkmodelle zugrunde legen. Bei einem Transistor z. B.

interessiert nur seine physikalische Wirkungsweise, die sich durch mathematische

Formeln angeben läßt. Mit Hilfe dieser Formeln und bestimmter Regeln, die

die Zusammenschaltung von Bauelementen beschreiben (Kirchhoffsche Regeln),

wird ein Gleichungssystem aufgestellt, das der Rechner (durch numerische

Verfahren) lösen kann. Mit Hilfe der Modellgleichungen kann der Rechner

die Ströme und Spannungen an allen interessierenden Punkten der Schaltung

(Netzwerkknoten) berechnen.

Da die einzelnen Modellgleichungen zumeist schon recht komplexer Natur

sind, sie enthalten z. B. gewöhnliche Differentialgleichungen, entstehen

bei der Zusammenstellung mehrerer Modelle im allgemeinen gekoppelte Differentialgleichungen,

die zur Lösung einige Rechenzeit benötigen.

B) Logiksimulationsprogramm

Bei diesem Programm geht man nicht mehr von einzelnen Bauelementen aus,

sondern von der nächsthöheren Einheit, den digitalen Schaltelementen. Dies

können einzelne Gatter sein oder bereits größere Einheiten, wie Flip-Flops

oder Speicher. Die Funktion dieser Elemente wird durch Tabellen beschrieben.

Bei der Logiksimulation werden diese Tabellen entsprechend der Zusammenschaltung

der digitalen Schaltelemente miteinander verknüpft.

Als Ergebnis der Rechnersimulation erhält man ein Signaldiagramm, aus dem

zu ersehen ist, welches Signal die Schaltung auf ein bestimmtes Eingangssignal

an ihrem Ausgang liefert, und welcher Zeitunterschied zwischen Eingang

und Ausgang besteht.

Da bei der Logiksimulation keine Gleichungssysteme, sondern nur Listen

verarbeitet werden müssen, liegt die Rechengeschwindigkeit wesentlich höher.

Logiksimulationsprogramme können daher für Schaltungen mit bis zu 107 Gatterfunktionen

eingesetzt werden.

Geometrischer Entwurf der Maskenvorlagen

Nachdem eine Schaltung entworfen, dimensioniert und durch ein Simulationsprogramm

auf ihre gewünschte Funktion getestet wurde, wird eine sog. Grobtopographie

entworfen. Dabei werden die ungefähre Lage der einzelnen Transistoren und

ihre Verbindungsleitungen untereinander

festgelegt. Man wird dabei versuchen, die Elemente so anzuordnen, daß Verbindungsleitungen

möglichst kreuzungsfrei gelegt werden können. Wo dies nicht möglich ist,

muß entschieden werden, ob eine Kreuzung durch Diffusionsgebiete „unterwandert“

wird oder über eine zweite Aluminiumebene erfolgen soll.

Anschließend wird mit Hilfe der Bauelementedimensionierung und bestimmter

Entwurfsregeln die Feintopographie erstellt. In der Feintopographie erhalten

die Diffusionsgebiete, Leiterbahnen und Gates ihre notwendigen Abmessungen.

Der nächste Schritt besteht nun darin, aus der Fein-topographie die Schaltzeiten

zwischen Ein- und Ausgängen zu berechnen und mit denen aus der Logiksimulation

zu vergleichen. Dies kann zu der Notwendigkeit führen, die Anordnungen

einzelner Transistoren zu ändern.

Das endgültige Layout, die fehlerlose Feintopographie, wird dann in einer

Datenbank gespeichert und dient schließlich zur Herstellung der Masken.

Die Zeichnung des Layout wird in erster Linie mit Hilfe von CAD durchgeführt,

da die immer wieder nötigen Änderungen der Topographie an einem Zeichenbrett

nicht bewältigt werden könnten. Da die Strukturen eines gesamten Layout

in der Größe eines Bildschirms jedoch nicht mehr erkannt werden können,

verwendet man zu Änderungsentscheidungen vergrößerte Ausschnitte des Layout,

die von einem Plotter ausgegeben werden. Diese Ausschnitte ergeben, zu

einem Ganzen zusammengefügt, Pläne in einer Größe von bis zu 50 m2. Dabei

werden die Topographien für die verschiedenen Masken übereinander gedruckt,

aber verschiedenfarbig dargestellt.

Da die meisten integrierten Schaltungen aus gleichartigen Elementen aufgebaut

sind, die nur entsprechend der geforderten Funktion verschieden verschaltet

werden müssen, werden häufig Strukturen von Gattern, Flipflops u. ä. in

einer „Bibliothek“ des Rechners abgelegt. Bei einer Neukonstruktion können

diese „vorstrukturierten Elemente“ abgerufen werden und brauchen nur noch

entsprechend plaziert und untereinander verbunden werden. Dadurch können

Entwicklungszeit und -kosten erheblich vermindert werden. Der Zeitraum

zwischen Entwicklung und Herstellung einer hochintegrierten Schaltung liegt

trotz dieser Vereinfachung üblicherweise bei vielen Monaten bis Jahren.

Entwurfstechnik an einem einfachen Beispiel

Es soll das Layout für ein statisches RS-Flipflop entwickelt werden. Zunächst

muß man die gewünschte Funktion der Schaltung definieren.

Funktionstabelle RS-Flipflop

Frame 5173

. Dabei ist t der Zeitpunkt der Ansteuerung eines Eingangs, t + 1 der Zeitpunkt

danach.

Wird am S-Eingang eine Spannung angelegt so soll der Ausgang Q ebenfalls

eine Spannung ausgeben. Der Zustand des Ausgangs soll erhalten bleiben,

auch wenn die Spannung am Eingang S wieder entfernt wird. Erst durch kurzzeitiges

Anlegen einer Spannung an den Eingang R soll der Ausgang Q in den spannungslosen

Zustand kippen. Durch wechselseitiges Ansteuern der Eingänge S (set) und

R (reset) ändert der Ausgang Q seinen jeweiligen Zustand. Man nennt eine

solche Schaltung daher bistabile Kippstufe oder englisch Flipflop. Da der

Ausgang Q seinen Zustand auch dann noch beibehält, wenn der entsprechende

Eingangsimpuls selbst bereits wieder verschwunden ist, bezeichnet man ein

Flipflop auch als digitales Speicherelement.

Die gewünschte Funktion des Flipflop läßt sich in einer Tabelle niederlegen,

wenn man den Zustand „Spannung“ mit 1 bezeichnet, den Zustand „keine Spannung“

mit 0, Tabelle oben. Man muß nun versuchen, die geforderte Funktion mit

Hilfe von bekannten Grundbausteinen der Digitaltechnik zu erfüllen. Eine

einfache Lösung stellt eine Verschaltung von sog. NOR-Gattern dar,Abbildung

8.

Funktionstabelle für NOR-Gatter

Frame 5166

Aus der Tabelle erkennt man, daß der Ausgang des NOR-Gatters 0 führt, sobald

mindestens an einem Eingang E eine 1 angelegt wird. Die Funktionsweise

der Schaltung nach Abbildung 8 läßt sich dann wie folgt beschreiben:

Beim Einschalten der Schaltung wird sich ein bestimmter, aber beliebiger

Zustand einstellen. Angenommen, der Ausgang von NOR 2 führt 0. Die Eingänge

R und S liegen ebenfalls auf 0. Da somit beide Eingänge von NOR 1 auf 0

liegen, führt dessen Ausgang eine 1. Diese 1 und die 0 vom Eingang R zwingen

den Ausgang von NOR 2 auf 0. Der Ausgang Q liegt stabil auf dem Zustand

0.

Wird nun an den Eingang S eine Spannung angelegt, so führt der eine Eingang

von NOR 1 den Zustand 0, der andere den Zustand 1. Der Ausgang von NOR

1 liegt somit auf 0. Die Kombination 0 und 0 an den Eingängen von NOR 2

läßt dessen Ausgang nun 1 führen. Die Eingangskombination von NOR 1 lautet

daher 1 und 1; am Ausgangszustand dieses NOR-Gatters ändert sich nichts.

Wird die Spannung am Eingang S wieder entfernt, so lautet die Eingangskombination

von NOR 2 1 und 0; der Ausgangszustand bleibt weiterhin erhalten. Der Ausgang

Q der Schaltung liegt auf dem stabilen Zustand 1. Durch Anlegen einer Spannung

an den Eingang R der Schaltung laufen die Kombinationen umgekehrt ab, der

Ausgang Q führt dadurch 0.

Man sieht, daß die Rückkopplung des Ausgangswertes auf die Eingänge wesentlich

zur Speicherfunktion und Stabilität beiträgt.

Die Schaltung erfüllt also die Funktionstabelle des RS-Flipflop. Bei einer

komplizierteren Schaltung wären solche Zustandsüberlegungen kaum noch möglich.

Man würde daher an dieser Stelle die Schaltung berechnen und mit einem

Rechner einen Logiktest durchführen. Ergibt sich daraus die Funktionstüchtigkeit

der Schaltung, so müssen im nächsten Schritt die NOR-Gatter durch Transistorschaltungen

ersetzt werden.

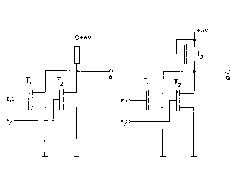

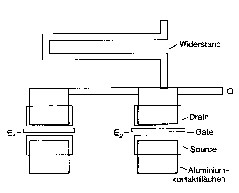

In Abbildung 9a erkennt man, daß der Ausgang Q beim Fehlen einer Eingangsspannung

über den Widerstand mit Spannung versorgt wird. Er führt daher log. 1.

Wird dagegen an wenigstens einem der beiden Eingänge EI und E2 eine Spannung

angelegt, so schaltet der entsprechende Transistor durch; der Ausgang Q

liegt direkt an 0 Volt, er führt log. 0.

Dieses Verhalten entspricht der Funktionstabelle. Durch entsprechende Verschaltung

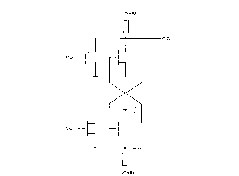

der Transistoren erhält man schließlich die Schaltung gemäß Abbildung 10.

Nach der Dimensionierung der einzelnen Bauelemente aus der Schaltung nach

Abbildung 10 kann nun das Layout begonnen werden.

Dazu wird zunächst auf dem Bildschirm des Rechners die Topographie eines

einzigen Transistors erstellt. Durch Verdoppelung bzw. Spiegelung und Neuplazierung

auf dem Bildschirm erhält man eine Topographie mit allen notwendigen Transistoren.

Diese müssen als Abschluß des Layout noch entsprechend Abbildung 10 mit

Leiterbahnen verbunden werden, Abbildung 11 und 12

In der ersten Generation elektronischer Bauteile, die bis in die sechziger

Jahre reichte, standen Bauelemente zur Verfügung, die jeweils nur eine

einzige definierte Eigenschaft hatten: Spulen als Induktivitäten, Kondensatoren

als Kapazitäten, Dioden als Gleichrichter, Widerstände, Transistoren als

Verstärker.

In der ersten Generation elektronischer Bauteile, die bis in die sechziger

Jahre reichte, standen Bauelemente zur Verfügung, die jeweils nur eine

einzige definierte Eigenschaft hatten: Spulen als Induktivitäten, Kondensatoren

als Kapazitäten, Dioden als Gleichrichter, Widerstände, Transistoren als

Verstärker.