Vorstellung des

Mikrocontrollerboard MikroWilliV1b8B

Allgemeine Beschreibung:

Ziel war es, ein

einfach aufzubauendes Mikrocontrollerboard zu entwickeln, welches von Schülern

ohne Probleme in der Werkstätte selbst aufgebaut wird und im Werkstättenlabor

in Betrieb genommen wird. Nach zahlreichen Prototypen entstand das vorliegende

Board. Jeder Prototyp wurde von mir persönlich aufgebaut, um kritische

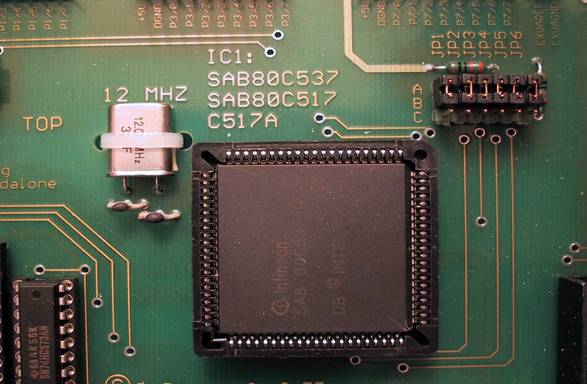

Arbeitsprozesse zu beseitigen. Als Controller sind die Typen SAB80C537,

SAB80C517(A) und C517A der Firma Infineon verwendbar. (C517A wurde noch nicht

getestet) Die Platine wurde bewusst nicht in Euroformat gefertigt, sondern ist

in Länge und Breite um ca. 20 mm grösser. Dadurch wurde eine unkritische

Bauteildichte

(Leiterbahnbreite und Abstand) erreicht. Die unbestückte Platine wird fertig

mit Durchkontaktierungen und Lötstopmaske geliefert. Es sind sämtliche

relevanten Anschlüsse auf Stiftleisten am Rand der Platine geführt. Jeder

Anschluss an den Stiftleisten ist beschriftet und zu jeder Einheit wurde die

Spannungsversorgung

+5V, und DGND ausgeführt. Bei der Positionierung der Stiftleisten wurde darauf

geachtet, dass das 100 mil Raster eingehalten wurde. Der Vorteil besteht darin,

dass man für Versuchsaufbauten normale Lochrasterplatinen verwenden kann.

(diese wird einfach aufgesetzt)

Auf dem Board MikroWilliV1b8B sind alle Komponenten vorhanden, die eine Entwicklung direkt auf der Zielhardware ermöglichen.

Und zwar sind dies folgende:

Spannungsversorgung

32k Eprom

32k Ram

Dekodierlogik ->

Von Neumann Architektur ab Adresse 0x8000 bis 0xFFFF

I/O Bereich, zum

Anschluß eigener Hardware

6 Jumper, zur

Einstellung des Betriebsmodus des Controllers

1 Jumper zur Auswahl

Debug oder Standalonebetrieb

1 Jumper, zur Auswahl

der Schnittstelle (UART0 oder UART1)

1 serielle Schnittstelle,

RS232(MAX242) -> UART0 für MasterSlaveModus geeignet

1 serielle

Schnittstelle, RS232(MAX232) -> UART1

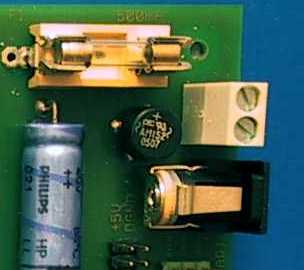

Spannungsversorgung..

Als

Spannungversorgung wurde ein 7805 verwendet, zur grösstmöglichen

Flexibilität und Sicherheit wurde ein Brückengleichrichter vorgeschalten.

Die Anschlüsse sind in zweifacher Ausführung vorhanden, nämlich als

Klinkenstecker (ist auf jedem Steckernetzteil vorhanden) und zweipoliger Printklemme. Man kann also jede Spannungsquelle im Breich von 8-18V egal ob Gleich.-oder

Wechselspannung verwenden. Das Board hat eine Stromaufnahme von ca. 100 mA.

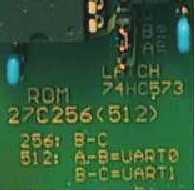

32kByte ROM-Speicher (27C256, *27C512)..

Er wird durch IC3

realisiert. Dieses EPROM enthält die vom Benutzer entwickelte Software, oder

ein Monitorprogramm. (z.B. Mon51 von Fa. Keil)

*27C512..

Um beim Wechsel der

seriellen Schnittstelle nicht das Eprom 27C256 auszutauschen, werden einfach

beide Monitore (für UART0 und UART1) in ein Eprom 27C512 gebrannt und mit JP10

(A15 am Eprom) wird die Auswahl getroffen.

32kByte RAM-Speicher (62256)..

Er wird durch IC4,

einen statischen RAM-Baustein realisiert. In ihm können Daten und Programme

abgelegt werden und auch ausgeführt werden. (Monitorbetrieb)

Dekodierlogik..

Harvard-Architektur

Die Schaltung wurde

so ausgelegt, um eigene Anwendungen auf der Zielhardware zu entwickeln. Die

MCS-51 Familie ist mit einer sogenannten Harvard-Architektur ausgestattet. Das heisst, Programmspeicher und Datenspeicher sind in streng

voneinander getrennten Speicherräumen untergebracht.

Von Neumann Architektur

Sie wird durch zwei NAND-Gattern des IC8 realisiert.

Diese Schaltung verknüpft das Lesesignal des Programmspeichers (PSEN) und das

Lesesignal des Datenspeichers (RD) zu einem neuen Lesesignal (NLS). Mit diesem

NLS Signal, ist das Lesen von Programm- und Datenbytes aus einem gemeinsamen

RAM-Speicherbereich

(8000h – FFFFh) möglich. Die Dekodierung des RAM‘s

wurde durch ein NAND-Gatter des IC8 realisiert. Das

ist nötig, um Programme mittels Monitor (Eprom) in das Ram zu laden

I/O Bereich, zum Anschluß eigener Hardware..

Er wird durch IC7,

einen 3-to-8 line

decoder/demultiplexer/invertierend

realisiert. Zur Dekodierung werden die Adressleitungen A12, A13, A14 und A15

verwendet. Es wurde bewusst auf den Einsatz eines Gals

verzichtet, um die Schaltung für Schüler überschaubar und so einfach wie

möglich zu gestalten. Eigene Hardware, z.B.

LCD-Display,

Digital to Analog-Converter (DAC) Porterweiterung mit

82C55 usw. wird wie RAM angesprochen. Die ChipSelect-Signale

sind LOW-AKTIV, dass heisst bei selektiertem

Adressbereich geht die geweilige Leitung von 1 nach

0.

Der I/O Bereich, von 0x0000 – 0x7FFF, ist in 8 Bereiche

unterteilt:

Signal Adressbereich

CS0 0x0000 – 0x0FFF

CS1 0x1000 – 0x1FFF

CS2 0x2000 – 0x2FFF

CS3 0x3000 – 0x3FFF

CS4 0x4000 – 0x4FFF

CS5 0x5000 – 0x5FFF

CS6 0x6000 – 0x6FFF

CS7 0x7000 – 0x7FFF

Jumpereinstellungen JP1-JP6 -> SAB80C537 -> Voreinstellungen* |

JP1 -> Referenz-Ground des ADC’s |

|

Jumper-Stellung |

Funktion

|

A-B* |

Interne Zuführung

(VAGND = DGND) |

|

B-C |

Externe Zuführung

(VAGND = EXVAGND) |

JP2 -> Referenzspannung des ADC’s |

|

Jumper-Stellung |

Funktion

|

|

A-B* |

Interne Zuführung

(VAREF = +5V) |

|

B-C |

Externe Zuführung

(VAREF = EXVAREF) |

JP3 ->

Hardware-Power-Down-Mode (HWPD)

|

|

Jumper-Stellung |

Funktion

|

|

A-B* |

DGND |

|

B-C |

wird nur von

SAB80C517A, C517A unterstützt |

JP4 -> Power-Down-Modi können nur per Software freigegeben werden (PE/SWD) |

|

Jumper-Stellung |

Funktion

|

|

A-B* |

Power-Down-Modi können nur per Software freigegeben

werden |

|

B-C |

Power-Down-Modi sind gesperrt, WDT startet

automatisch nach dem Reset. |

JP5 -> Oszillator-Watchdog (OWE) |

|

Jumper-Stellung |

Funktion

|

|

A-B* |

Der Oszillator-Watchdog ist ausgeschalten |

B-C

|

Der Oszillator-Watchdog ist freigegeben |

JP6 -> Externer oder interner Programmspeicher-Zugriff (EA) |

|

Jumper-Stellung |

Funktion

|

A-B*

|

externer

Programmspeicher-Zugriff |

|

B-C |

interner

Programmspeicher-Zugriff |

Jumpereinstellungen A, B, C* |

Harvard oder VonNeumann Architektur |

|

Jumper-Stellung |

Funktion

|

A-B* |

Test

auf Zielhardware: Von Neumann-Architektur

Monitor: 0x0000

– 0x7FFF 32k Eprom Programm oder

Datenspeicher: 0x8000 – 0xFFFF 32k Ram I/O Bereich: 0x0000 –

0x7FFF 32k |

A-C

|

Normal-Betrieb: Harvard -Architektur Eigenes

Programm: 0x0000 – 0x7FFF 32k Eprom Datenspeicher: 0x8000 – 0xFFFF

32k Ram I/O Bereich: 0x0000 –

0x7FFF 32k |

UART0, UART1..

Da einige Mitglieder

Mcs-51 Familie SAB80C537, SAB80C517, C517A,

Dallas 80C320 usw.,

zwei serielle Schnittstellen besitzen, wurden diese auch ausgeführt. Dies

erwies sich als richtige Entscheidung, da über die eine das Programm in die

Zielhardware übertragen wird und über die zweite zum Beispiel Messdaten zum PC

gesendet werden können. Als Pegelumsetzer wurde für UART1 ein normaler MAX232

verwendet. Da aber alle Mitglieder der MCS-51 Familie

Intel 80C31, Intel

80C32, Atmel 89C..., Dallas.. usw. einen sogenannten Master-Slave-Modus unterstützen, (Modus 2, Modus 3) wurde um

die Kompatibilität zu wahren auf UART0 ein MAX242 verwendet. Um ein

Multiprozessorsystem aufzubauen, eignet sich der MAX242 besonders, da er in der

Lage ist, seine Sendetreiber auf der RS232-Seite abzuschalten. Dabei bleibt der

Empfänger aber aktiv. Über eine Portleitung (P6.3) wird die Senderfreigabe über

den Anschluss SHUTDOWN gesteuert.

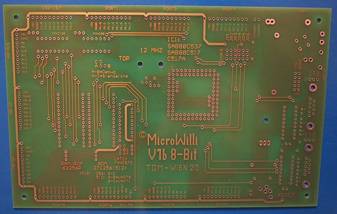

Zum Abschluss einige Fotos: von MicroWilli

Foto der unbestückten

Platine:

Foto der bestückten

Platine: Bestückungsseite

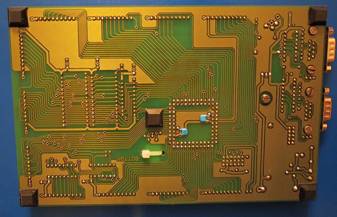

Foto der bestückten

Platine: Lötseite